9. CMOSによる基本論理回路

CMOS(Complementary Metal-Oxide-Semiconductor)論理回路は、金属酸化膜半導体(MOS)FETのP型とN型を組み合わせた論理回路構成の方式で、ディジタル回路で広く使用される集積回路技術の一つとなっている。CMOS論理回路は、TTL論理回路に比べて、消費電力が小さく、高速動作が可能という特徴がある。また、動作電圧が+3.3Vと低電圧化されているため、バッテリ駆動の携帯機器などにも用いられている。CMOS論理回路の特徴は、消費電力が小さい、高速動作が可能、動作電圧が低い、ノイズに強い、集積度が高い、である。これらの特徴により、CMOS論理回路は、ディジタル論理回路やメモリセルなど広範なアプリケーションに適している。

(FETについては、電界効果トランジスタ(FET)を参照して欲しい。)

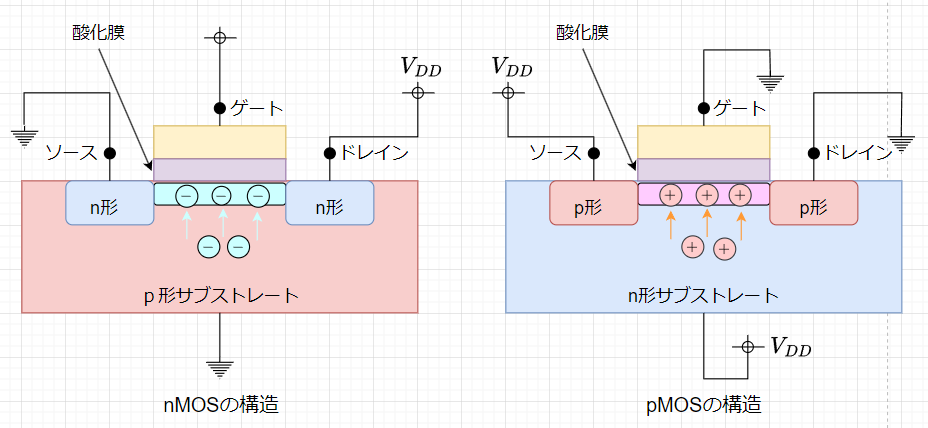

MOS-FETの構造

図1にMOS-FETの構造を示す。nMOS-FETの場合、p形半導体のサブストレート(基板or台座)にn形の領域を二つ作る。p形半導体の多数キャリアは正孔、n形半導体の多数キャリアは電子である。n形の領域は、ソースとドレイン端子を接続する。ソース、ドレインのn形領域の間に薄い酸化膜で絶縁された導電体(ポリシリコン)を置き、ゲート端子に接続する。図のようにドレイン、ソース間に電圧をかけた場合、ゲートに電圧をかけない状態(ゲート電圧を\(GND\))では、ソース、ドレイン間のp形半導体により、ドレイン側のpn接合が逆バイアスになるため、電流が流れない。この状態がnMOS-FETのOFF状態である。p形のサブストレートの多数キャリアは正孔であるが、少数キャリアとして電子がある。従って、ゲートに電圧をかけると(ゲート電圧を\(V_{DD}\))、ゲートの電界により、電子がゲート直下に引き寄せられ電子が多数キャリアとなるn形の領域が形成される。この領域を反転層という。この反転層により、ドレイン、ソース間が繋がり、電流が流れるようになる。この状態がnMOS-FETのON状態である。

図1のpMOS-FETの場合、n形半導体のサブストレートにp形の領域を二つ作る。p形の領域は、ソースとドレイン端子を接続する。ソース、ドレインのp形領域の間に薄い酸化膜で絶縁された導電体(ポリシリコン)を置き、ゲート端子に接続する。図のようにソース、ドレイン間に電圧をかけた場合、サブストレート側に対してゲート電圧が低くない状態(ゲート電圧を\(V_{DD}\))では、ソース、ドレイン間のn形半導体により、ソース側のpn接合が逆バイアスになるため、電流が流れない。この状態がpMOS-FETのOFF状態である。n形のサブストレートの多数キャリアは電子であるが、少数キャリアとして正孔がある。従って、サブストレート側に対してゲート電圧を低くすると(ゲート電圧を\(GND\))、ゲートの電界により、正孔がゲート直下に引き寄せられ正孔が多数キャリアとなるp形の領域(反転層)が形成される。この反転層により、ソース、ドレイン間が繋がり、電流が流れるようになる。この状態がpMOS-FETのON状態である。

MOS-FETの回路図記号と特性

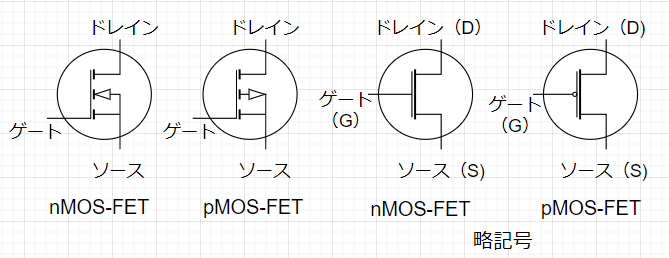

図2にエンハンスメント形のMOS-FETの標準的な回路図記号と略記号を示す。

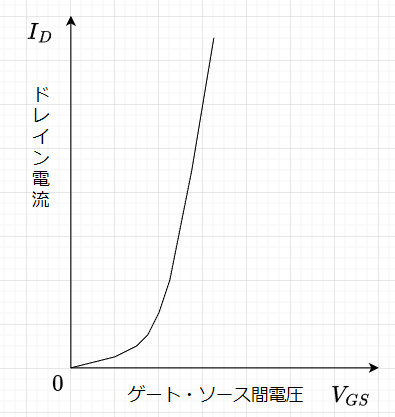

図3は、エンハンスメント形のnMOS-FETの\(V_{GS} - I_D\)特性である。ゲート・ソース間\(V_{GS}\)に正の電圧を掛けるとソース・ドレイン間がON状態になり、ドレイン電流\(I_D\)が流れる。\(V_{GS}\)を\(0 \;V\)にするとソース・ドレイン間はOFF状態になる。

以上の構造、及び特性からnMOS、pMOSは、つぎの簡単なモデルで動作を近似できる。

nMOS:ゲートにHレベルを与えると、FETはONになり、Lレベルを与えるとOFFになる。FETがONのときには、ソース・ドレイン間は導通し、OFFのときは開放となる。

pMOS:ゲートにLレベルを与えると、FETはONになり、Hレベルを与えるとOFFになる。FETがONのときには、ソース・ドレイン間は導通し、OFFのときは開放となる。

MOS-FETでは、ON時でもOFF時でもゲートには、ほとんど電流が流れず、ゲート側から見た入力インピーダンスは非常に大きい。従って、MOS-FETの近似モデルは、理想的なスイッチと考えることができる。

なお、Hレベルは電源電圧\(V_{DD}\)(\(5\;V\)、\(3.3\;V\)、\(1.8 \;V\)など)、Lレベルは\(GND\)(\(0\;V\)に近い電圧)と考えるものとする。

エンハンスメント形

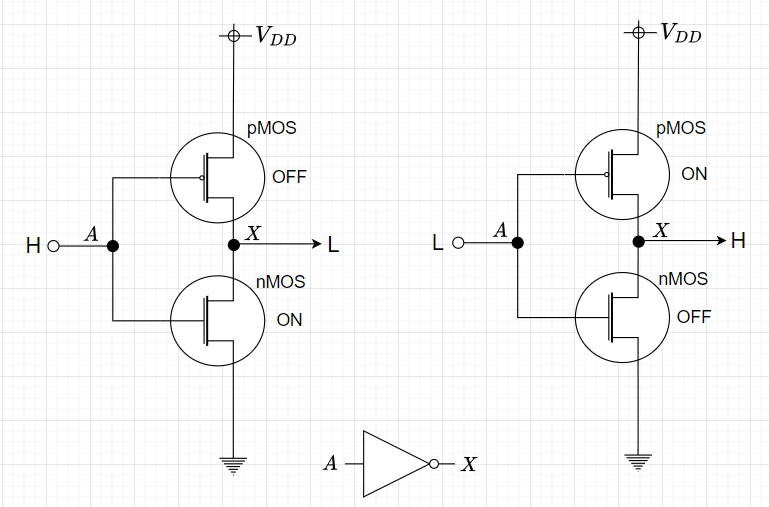

CMOSによるNOT回路

CMOSの論理回路構成では、nMOSとpMOSのFETを相補的に組み合わせる。つまり、nMOSがONのときは、pMOSがOFFとなり、nMOSがOFFのときは、pMOSがONとなるペアの単位で組み合わせて論理回路を構成する。

図4は、nMOSとpMOSを組み合わせたCMOSによるNOT回路である。nMOSとpMOSそれぞれのFETのゲートが共通になっており、入力\(A\)がHレベルの場合は、nMOSがONにpMOSがOFFとなり、出力\(X\)はLレベルとなる。入力\(A\)がLレベルの場合は、nMOSがOFFにpMOSがONとなり、出力\(X\)はHレベルとなる。つまり、NOT回路となっている。

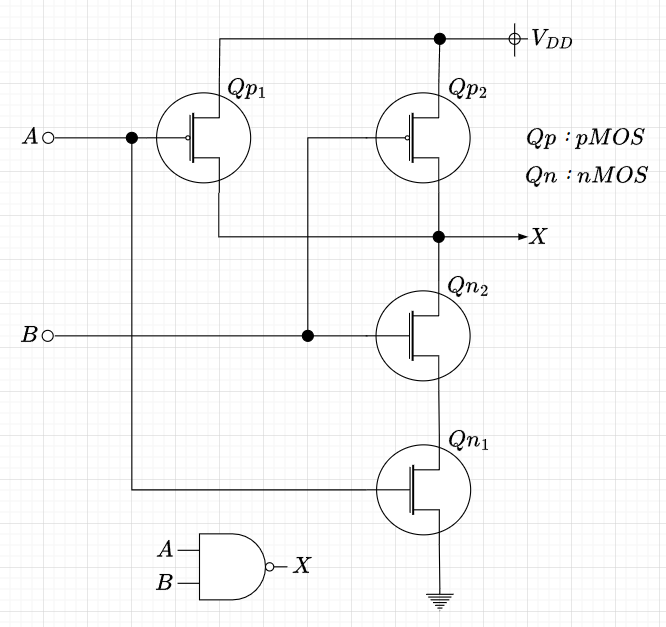

CMOSによるNAND回路

図5は、nMOSとpMOSを組み合わせたCMOSによるNAND回路である。pMOSは並列、nMOSは直列に接続され、\(Qp_1\)と\(Qn_1\)、\(Qp_2\)と\(Qn_2\)のゲートがそれぞれ接続されており、片方がONのときには、もう一方はOFFとなる。表1に動作表を示す。この動作表より、このCMOS論理回路がNAND回路であることが分かる。

| \(A\) | \(B\) | \(Qp_1\) | \(Qp_2\) | \(Qn_1\) | \(Qn_2\) | \(Y\) |

| L | L | ON | ON | OFF | OFF | H |

| L | H | ON | OFF | OFF | ON | H |

| H | L | OFF | ON | ON | OFF | H |

| H | H | OFF | OFF | ON | ON | L |

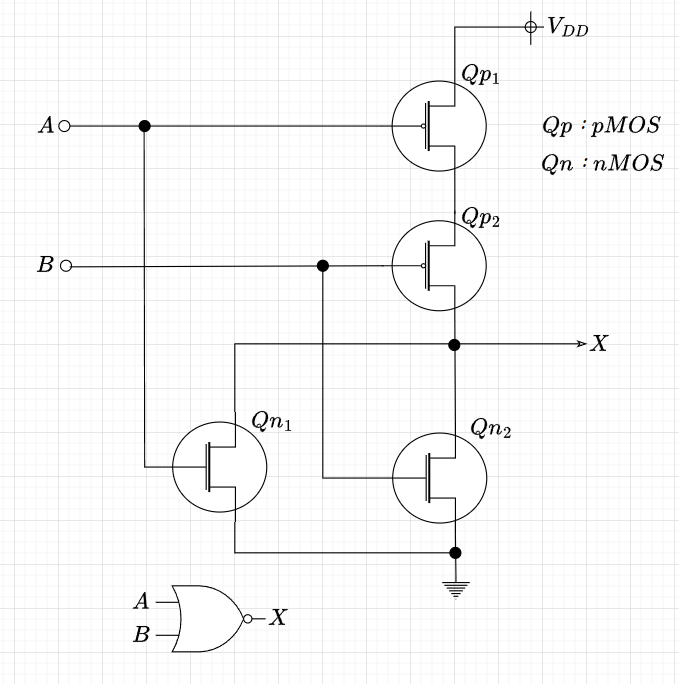

CMOSによるNOR回路

図6は、nMOSとpMOSを組み合わせたCMOSによるNOR回路である。pMOSは直列、nMOSは並列に接続され、\(Qp_1\)と\(Qn_1\)、\(Qp_2\)と\(Qn_2\)のゲートがそれぞれ接続されており、片方がONのときには、もう一方はOFFとなる。表2に動作表を示す。この動作表より、このCMOS論理回路がNOR回路であることが分かる。

| \(A\) | \(B\) | \(Qp_1\) | \(Qp_2\) | \(Qn_1\) | \(Qn_2\) | \(Y\) |

| L | L | ON | ON | OFF | OFF | H |

| L | H | ON | OFF | OFF | ON | L |

| H | L | OFF | ON | ON | OFF | L |

| H | H | OFF | OFF | ON | ON | L |

“9. CMOSによる基本論理回路” に対して1件のコメントがあります。

コメントは受け付けていません。