10. パストランジスタロジック

パストランジスタロジック(Pass Transistor Logic:PTL)は、ディジタル論理回路の一種で、トランジスタをスイッチとして使用し、データパス(信号パス)を制御する方式である。これは、CMOS論理回路と比較して少ないトランジスタ数で論理回路を実現できる場合が多い。パストランジスタロジックは、NAND、NORなどの単純な関数については、CMOS論理が有利となる場合が多いが、XORやMUX(マルチプレクサ)などのより複雑な関数については、パストランジスタロジックがトランジスタ数の点で有利となる。パストランジスタロジックが、すべての回路に対してCMOS論理回路より有利とは限らない。従って、実現すべき関数の種類に応じてCMOSとパストランジスタロジックを使い分けて回路を構成することが考えられる。

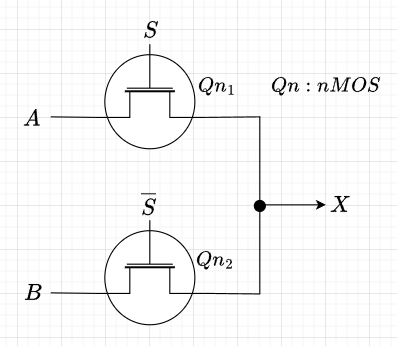

nMOSによるデータセレクタ

MOS-FETの構造を見てわかるように、ドレインとソースは同じ構造になっており、どちらの方向にも電流を流すことができる。この機能を利用して、図1のような回路を構成できる。この回路は、nMOSだけを使ったデータセレクタである。\(S\)をHにすると、\(Qn_1\)がON、\(Qn_2\)がOFFとなり、\(A\)が\(X\)に出力される。\(S\)をLにすると、\(Qn_1\)がOFF、\(Qn_2\)がONとなり、\(B\)が\(X\)に出力される。このように利用されるFETのことをパストランジスタと呼び、パストランジスタのON/OFF機能を利用して構成した回路をパストランジスタロジック(PTL)と呼ぶ。

図1の回路には問題点がある。つまりnMOS-FETは、Lレベルの伝送は高速であるが、Hレベルでは伝送遅延が大きい。これには、複数の要因が関係し、以下が考えられる。

・電子移動の遅れ: nMOSトランジスタは、電子がゲートの正の電界の方向に動くため、電子の移動には一定の時間がかかる。

・キャパシタンス効果: nMOSトランジスタのソースとドレインの間には容量があり、この容量が電荷の移動に影響を与え、伝送遅延を引き起こす。

pMOS-FETは、反対にHレベルの伝送は高速であるが、Lレベルでは伝送遅延が大きい。

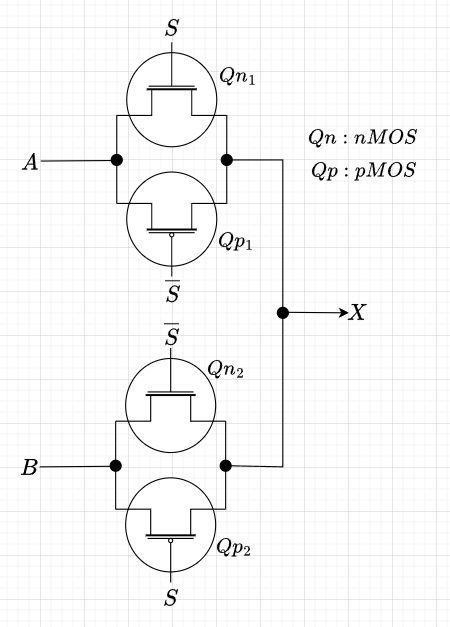

CMOSによるデータセレクタ

nMOSだけのPTLの問題を解消する方式として、図2のようにpMOSとnMOSを組み合わせる。このような構成にすることで、Lレベルの伝送では、nMOSが主に働き、Hレベルの伝送では、pMOSが主に働くので、両方のレベルでの高速な伝送が可能になる。このpMOS-nMOSの1セットをトランスミッションゲート(伝送ゲート)と呼ぶ。\(S\)をHにすると、\(Qn_1, \;Qp_1\)がONとなり、\(A\)が\(X\)に出力される。\(S\)をLにすると、\(Qn_2, \;Qp_2\)がONとなり、\(B\)が\(X\)に出力される。

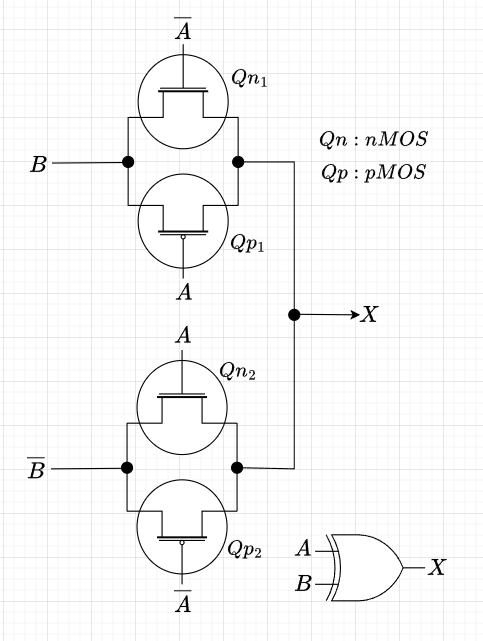

パストランジスタロジックによるEXOR

図3は、トランスミッションゲートを使ったPTLによるEXOR回路である。表1に動作表を示す。このようにPTLを使うことで、基本的なCMOS論理回路では実装が複雑になる回路を容易に実現することができる。

| \(A\) | \(B)\ | \(Qp_1\) | \(Qp_2\) | \(Qn_1\) | \(Qn_2\) | \(X\) |

| L | L | ON | OFF | ON | OFF | L |

| L | H | ON | OFF | ON | OFF | H |

| H | L | OFF | ON | OFF | ON | H |

| H | H | OFF | ON | OFF | ON | L |