16. カウンタ

カウンタ回路は、周波数や時間などをカウントする回路で、フリップフロップや論理ゲートなどを組み合わせて構成する。カウンタ回路には、大きく分けてアップカウンタ、ダウンカウンタの2種類がある。カウンタ回路の応用例としては、時計、タイマー、周波数計、メトロノームなどがある。時計は、例えば、1秒ごとにカウンタ回路を1カウントさせて時間を表示する。メトロノームは一定のテンポで音を鳴らすためにカウンタ回路が使われる。このように、カウンタ回路はさまざまな電子機器やシステムの基本的な構成要素として欠かせない回路である。

2進カウンタ

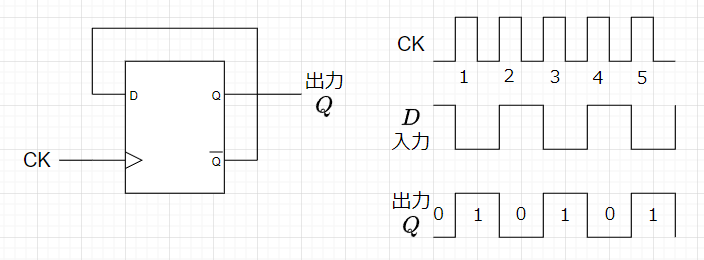

図1は最も基本的なカウンタで、Dフリップフロップの出力\(\overline{Q}\)を入力\(D\)に戻すと、クロック(\(CK\)が入る度に出力\(Q\)が反転する。Lを0、Hを1に対応させると、表1のカウント表のように表せる。この表を見ると、\(CK\)が2つ入ると元の状態になるので、2進数の1桁の動作となっていることが分かる。これを2進カウンタという。

| \(CK\)の数 | 2進表示 (出力\(Q\)) |

| 0 | 0 |

| 1 | 1 |

| 2 | 0 |

| 3 | 1 |

| 4 | 0 |

| 5 | 1 |

4進カウンタ(非同期式)

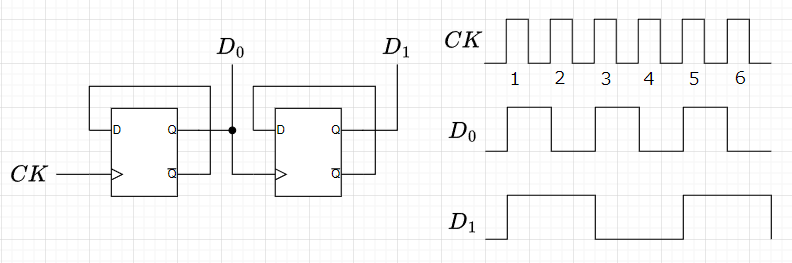

図2に示すように、1段目の2進カウンタの出力\(Q\)を2段目の\(CK\)に接続することで、4進カウンタとなる。図2(右)がタイミングチャートである。また、カウント表は表2のようになる。10進表示を見ると、\(0 \rightarrow 3 \rightarrow 2 \rightarrow 1 \rightarrow 0\)のように変化している。つまり、この4進カウンタは4進のダウンカウンタ(カウント数が減っていくカウンタ)となっていることが分かる。

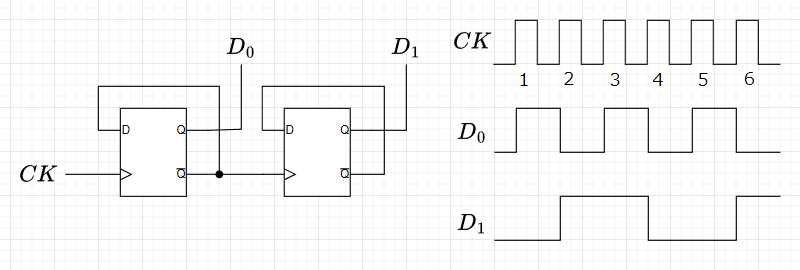

図3に示すように、1段目の2進カウンタの出力\(\overline{Q}\)を2段目の\(CK\)に接続すると4進のアップカウンタになる。図3(右)がそのタイミングチャートである。また、カウント表は表3のようになる。10進表示を見ると、\(0 \rightarrow 1 \rightarrow 2 \rightarrow 3 \rightarrow 0\)のように変化している。つまり、この4進カウンタは4進のアップカウンタ(カウント数が順に増えていくカウンタ)となっていることが分かる。

以上のように、フリップフロップを直列に接続することで、\(2^n\)進カウンタを構成できる。しかしながら、各フリップフロップの\(CK\)端子には、前段の出力が接続される形になっているので、各素子の遅延時間により、後段になるほど最初のクロック(カウントしたいクロック)のタイミングから遅れることになる。このようなカウンタを非同期式カウンタという。このような非同期式カウンタの場合、カウントしたいクロックに対して、各段の出力(\(D_0,D_1,D_2,\cdots\))の変化が同時に起こらないことに注意する必要がある。

| \(CK\)の数 | \(D_1\) | \(D_0\) | 10進表示 |

| 0 | 0 | 0 | 0 |

| 1 | 1 | 1 | 3 |

| 2 | 1 | 0 | 2 |

| 3 | 0 | 1 | 1 |

| 4 | 0 | 0 | 0 |

| 5 | 1 | 1 | 3 |

| 6 | 1 | 0 | 2 |

カウント表

| \(CK\)の数 | \(D_1\) | \(D_0\) | 10進表示 |

| 0 | 0 | 0 | 0 |

| 1 | 0 | 1 | 1 |

| 2 | 1 | 0 | 2 |

| 3 | 1 | 1 | 3 |

| 4 | 0 | 0 | 0 |

| 5 | 0 | 1 | 1 |

| 6 | 1 | 0 | 2 |

カウント表

\(2^n\)進同期式カウンタ

各フリップフロップの出力が、クロック入力に同期して変化するように構成したカウンタを同期式カウンタという。同期式カウンタは回路は複雑になるが、出力が同時に変化するので、タイミングの考え方は簡単になる。

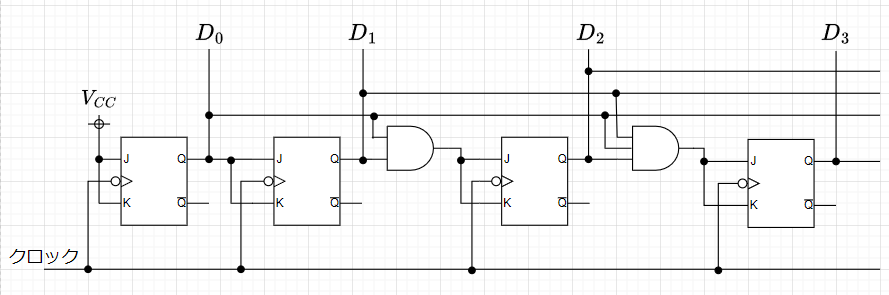

図4は、JK-FFを4個使った16進同期式カウンタの例である。図のようにJ、K端子を接続することで、J、K入力が1のとき出力が反転し、J、K入力が0のとき出力が反転しないようにAND素子を使うことで実現している。この構成は、後段になるほどANDの素子数が増えるので回路が複雑になるが、クロックに同期でき、動作速度も速い構成である。

この構成の接続を拡張することで\(2^n\)進同期カウンタが実現できる。

| クロック数 | \(D_3\) | \(D_2\) | \(D_1\) | \(D_0\) |

| 0 | 0 | 0 | 0 | 0 |

| 1 | 0 | 0 | 0 | 1 |

| 2 | 0 | 0 | 1 | 0 |

| 3 | 0 | 0 | 1 | 1 |

| 4 | 0 | 1 | 0 | 0 |

| 5 | 0 | 1 | 0 | 1 |

| \(\vdots\) | \(\vdots\) | \(\vdots\) | \(\vdots\) | \(\vdots\) |

カウント表(6以降は省略)

10進カウンタ

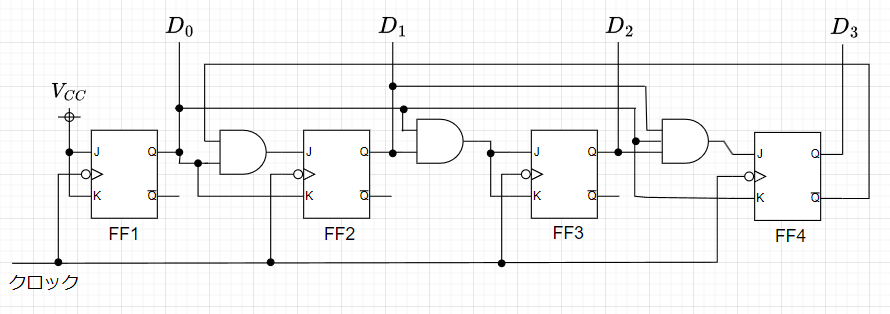

図5はJK-FFを使った10進同期式アップカウンタの回路図である。図4の16進同期式カウンタを基本にして、表5に示すように10クッロク目で出力\(D_3,D_2,D_1,D_0\)が\(0000\)となるように回路を修正すれば良い。

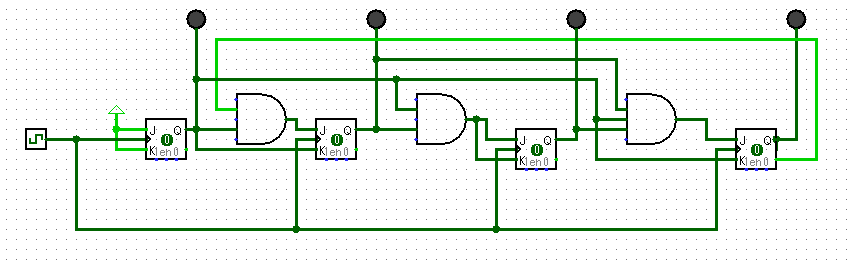

図6は論理回路シミュレータ(Logisim)を使ったシミュレーション回路図である。

シミュレーション

(Logisim)

Logisim

Logisimのサイト:http://www.cburch.com/logisim/

Logisimの使い方:https://www.slideshare.net/takashikawanami/logisim-39730181

| クロック数 | \(D3\) | \(D2\) | \(D1\) | \(D0\) |

| 0 | 0 | 0 | 0 | 0 |

| 1 | 0 | 0 | 0 | 1 |

| 2 | 0 | 0 | 1 | 0 |

| 3 | 0 | 0 | 1 | 1 |

| 4 | 0 | 1 | 0 | 0 |

| 5 | 0 | 1 | 0 | 1 |

| 6 | 0 | 1 | 1 | 0 |

| 7 | 0 | 1 | 1 | 1 |

| 8 | 1 | 0 | 0 | 0 |

| 9 | 1 | 0 | 0 | 1 |

| 10 | 1\(\rightarrow\)0 | 0 | 1\(\rightarrow\)0 | 0 |

カウント表