14. マルチプレクサ、デマルチプレクサ

マルチプレクサ(Multiplexer)とデマルチプレクサ(Demultiplexer)は、デジタル回路や通信システムなどで使用される基本的な論理回路である。マルチプレクサは、複数のデータ入力ラインから選択した1つのデータ出力ラインにデータを送るための回路で、MUX(略称)と呼ばれる。デマルチプレクサは、1つのデータ入力ラインから選択した複数のデータ出力ラインにデータを送るための回路で、主にDEMUX(略称)と呼ばれる。マルチプレクサとデマルチプレクサは通信やデータ処理の場面で広く使用され、データの集約や分配など、異なるデータストリームの管理に役立つ。

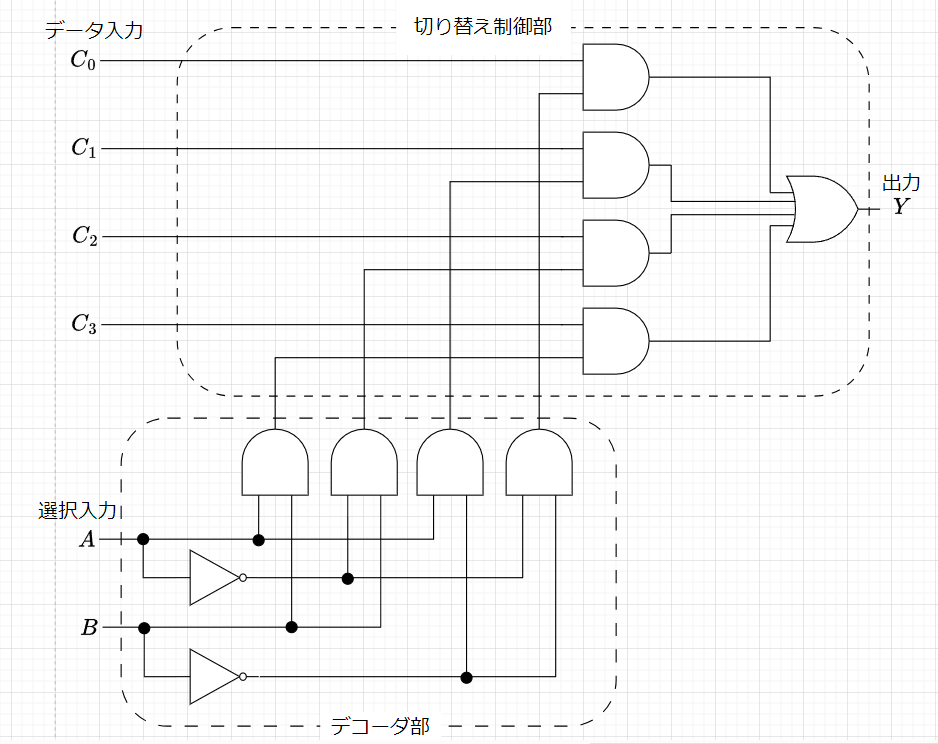

マルチプレクサ(MUX)

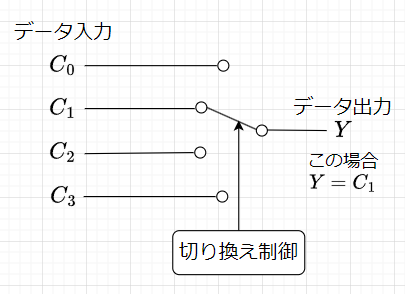

図1は、マルチプレクサの基本構成図である。一般的なn-to-1 マルチプレクサの構成では、nを入力ラインの数、m を制御信号のビット数とすると、選択信号がm ビットの場合、マルチプレクサは2^m個の異なる入力の中から1つを選択することになる。n=4、m=2とした具体的なMUXの論理回路例を図2に示す。表1は、図2のMUXの動作表である。

| 選択入力 | 選択入力 | 出力 |

| B\;\;\;\;\; 2^1 | A\;\;\;\;\;\;2^0 | Y |

| 0 | 0 | C_0 |

| 0 | 1 | C_1 |

| 1 | 0 | C_2 |

| 1 | 1 | C_3 |

デマルチプレクサ(DEMUX)

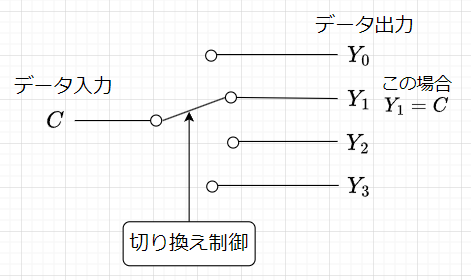

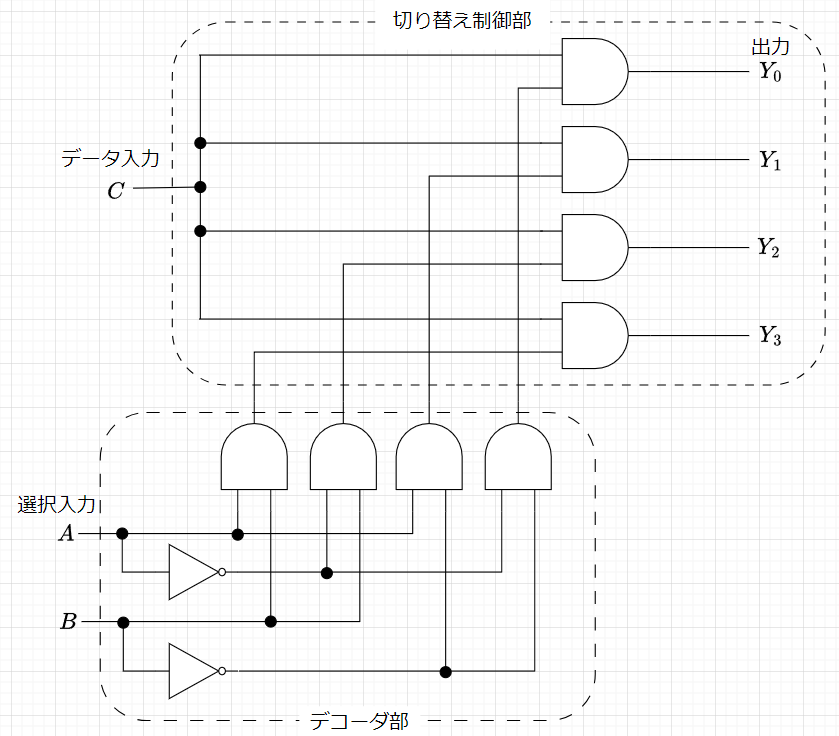

図3は、デマルチプレクサの基本構成図である。一般的な 1-to-n デマルチプレクサの構成である。n は出力ラインの数を表す。デマルチプレクサは、制御信号によって選択された出力ラインにのみデータを送る。具体的なDEMUXの論理回路例を図4に示す。表2は、図4のDEMUXの動作表である。

| 選択入力 | 選択入力 | 出力 |

| B\;\;\;\;\; 2^1 | A\;\;\;\;\;\;2^0 | |

| 0 | 0 | Y_0 |

| 0 | 1 | Y_1 |

| 1 | 0 | Y_2 |

| 1 | 1 | Y_3 |